技术参数

| 品牌: | TI(德州仪器) |

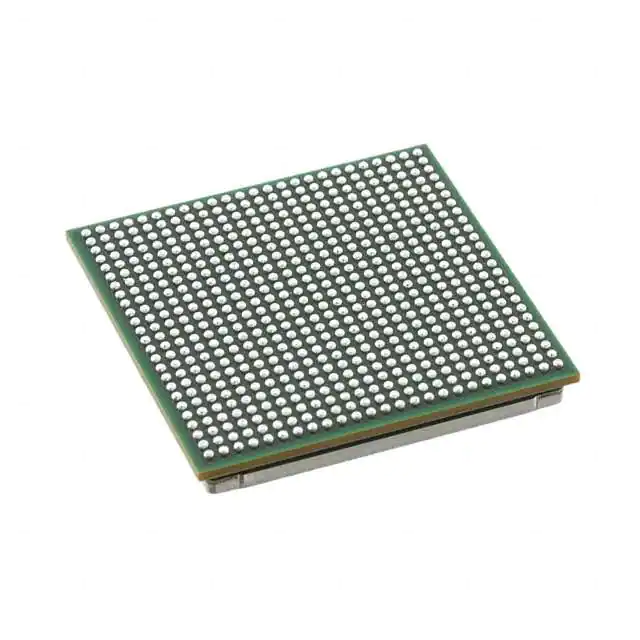

| 型号: | TMS320C6657CZH25 |

| 封装: | FCBGA-625(21x21) |

| 批号: | 23+ |

| 数量: | 5000 |

| 制造商: | Texas Instruments |

| 产品种类: | 数字信号处理器和控制器 - DSP, DSC |

| RoHS: | 是 |

| 安装风格: | SMD/SMT |

| 封装 / 箱体: | FCBGA-625 |

| 系列: | TMS320C6657 |

| 核心: | C66x |

| 最大时钟频率: | 1 GHz, 1.25 GHz |

| 程序存储器大小: | 128 kB |

| 数据 RAM 大小: | 3 MB |

| 工作电源电压: | 900 mV to 1.1 V |

| 最小工作温度: | - 40 C |

| 最大工作温度: | + 100 C |

| 接口类型: | EMAC, I2C, Hyperlink, PCIe, RapidIO, UPP |

| 输入/输出端数量: | 32 I/O |

| 数据总线宽度: | 32 bit |

| MMACS: | 80000 MMACS |

| 湿度敏感性: | Yes |

| 计时器/计数器数量: | 10 Timer |

| 电源电压-最大: | 1.1 V |

| 电源电压-最小: | 900 mV |

| 单位重量: | 4.886 g |

C665x是基于Tl的KeyStone多体系结构的高性能定点和浮点DSP。结合新的和创新的C66x DSP核心,该设备可以运行在一个核心速度高达1.25千兆赫。对于广泛应用程序的开发人员来说,C665x DSP都支持一个节能且易于使用的平台。此外,C665x DSP完全向后兼容所有现有的C6000n系列固定和浮点DSP。I的KeyStone体系结构提供了一个集成各种子系统(C66x coresmemory子系统、外围设备和加速器)的可编程平台,并使用若干创新组件和技术最大化设备内和设备间通信,使各种DSP资源高效无缝地运行。该体系结构的核心是关键组件,如MultiRenaviator,它允许在各种设备组件之间进行有效的数据管理。TeraNets是一种非阻塞交换结构,支持快速和无争用的内部数据移动,多线程共享内存控制器允许直接访问共享和外部内存,而无需使用交换机结构容量。

对于定点使用,C66x内核具有C64x+内核的4倍乘法累加(MAC)能力。此外,C66x core集成浮点功能,每核原始计算性能为业界领先的每核40 GMAC,每核20 GFLOPS(@1.25 GHz工作频率)。C66x内核每周期可执行8个单精度浮点MAC操作,并可执行双精度和混合精度操作,符合IEEE 754标准。C66x内核包含90条新指令(与C64x+内核相比),用于浮点和面向向量的数学处理。这些增强在用于信号处理、数学和图像采集功能的常用DSPKernel中产生了相当大的性能改进。C66x内核是向后代码,与Tl上一代C6000定点和浮点DSP内核兼容,确保了软件的可移植性,缩短了应用程序迁移到主硬件的软件开发周期。

C665x DSP集成了大量的片上存储器。除了32KB的一级程序和数据缓存,1024KB的专用内存可以配置为映射RAM或缓存。该设备还集成了1024KB的多核共享内存,可用作共享L2 SRAM和/或共享L3SRAM。所有L2存储器包括错误检测和错误校正。为了快速访问外部内存,该设备包括一个32位DDR-3外部内存接口(EMIF),以1333MHz的速率运行,并支持ECC DRAM。

该系列支持许多高速标准接口,包括RapidlO ver 2、PCI ExpressGen2和千兆以太网。该系列DSP还包括1C、UART、多通道缓冲串行端口(McBSP)、通用并行端口(uPP)和16位异步EMIF,以及通用CMOS 10。对于设备之间或与FPGA之间的高吞吐量、低延迟通信,包括一个名为HyperLink的40.Gbaud全双工接口。

C665x设备有一套完整的开发工具,包括:一个增强的C编译器、一个简化编程和调度的汇编优化器,以及一个用于查看源代码执行情况的Windows@debugger接口。

I的KeyStone多核体系结构为RISC和DSPcores与特定于应用程序的协处理器和1/0集成提供了高性能结构。KeyStone体系结构是同类体系结构中的第一个,它提供了足够的内部带宽,以便对所有处理核心、外围设备处理器和I/0进行非阻塞访问。这种内部带宽由四个主要硬件元素实现:MultiRenaviator、TeraNet、多核共享内存控制器和HyperLink。

Multicore Navigator是一种创新的基于数据包的管理器,可控制8192个队列。当任务分配到队列时,多核导航器提供硬件加速调度,将任务定向到适当的可用硬件。基于分组的片上系统(SoC)使用TeraNet交换中心资源的两个Tbps容量来移动分组。多核共享内存控制器允许处理核直接访问共享内存,而无需利用TeraNet的容量,因此数据包的移动不受内存访问的阻碍。

HyperLink提供了一个40 Gbaud芯片级互连,允许SOC串联工作。HyperLink的低协议覆盖率和高吞吐量为芯片间互连提供了理想的接口。HyperLink使用多核导航器将任务透明地分配给串联设备,并像在本地资源上运行一样执行任务。

尖货爆款

尖货爆款

海量现货 种类齐全

海量现货 种类齐全

快速报价 闪电出库

快速报价 闪电出库

原厂渠道 原装正品

原厂渠道 原装正品

优势价格 节省成本

优势价格 节省成本

专属客服 FAE支持

专属客服 FAE支持